August 29, 2014, Rev. -

### **General Description**

The AXI 7 Series DDRx (Limited) DO-254 Certifiable Data Package is made up of the artifacts produced by applying the DO-254 lifecycle to the Xilinx® AXI 7 Series DDRx IP v1.07a and an encrypted version of the source code. This includes the following completed documents:

- Plan for Hardware Aspects of Certification

- Hardware Validation and Verification Plan

- Hardware Configuration Management Plan

- Hardware Design Plan

- Hardware Process Assurance Plan

- Hardware Validation and Verification

Standard

- Hardware Requirements Standard

- Hardware Design Standard

- Hardware Requirements Document

- Hardware Design Document

- Hardware Configuration Index (includes Hardware Lifecycle Environment Configuration Index)

- Verification Configuration Index

- Hardware Test Procedures

- Hardware Verification Results

- Hardware Elemental Analysis Results

- Hardware Requirements Traceability

Matrix

- Hardware Accomplishment Summary

The above documents are available for certification efforts, however not all documents are included in the delivery package.

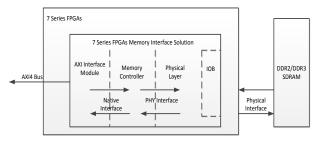

The DO-254 AXI 7 Series DDRx (Limited) IP Core 1.00a, created and designed by Logicircuit, is a combined pre-engineered controller and physical layer (PHY) for interfacing 7 series FPGA user designs and AMBA<sup>®</sup> advanced extensible interface (AXI4) slave interfaces to DDR3 and DDR2 SDRAM devices.

This version of the DO-254 AXI 7 Series DDRx (Limited) IP includes the following built-in safety features:

• Error Correcting Code (ECC), for DDR3 memories with 72 bits data width.

#### Features

- 8-bank support

- 8-word burst support

- 4:1 and 2:1 memory to FPGA logic interface clock ratio

- On-die termination (ODT) support

- I/O Power Reduction option reduces average I/O power by automatically disabling DQ/DQS IBUFs and internal terminations during writes and periods of inactivity

- Two controller request processing modes:

- Normal: reorder requests to optimize system throughput and latency

- Strict: memory requests are processed in the order received

DDR3 SDRAM specific features:

- ECC support

- Configurable data bus widths (doubles from 8, up to 72 bits)

- Support for 5 to 13 cycles of columnaddress strobe (CAS) latency (CL)

- Support for 5 to 9 cycles of CAS write latency

JEDEC-compliant DDR3 initialization support

DDR2 SDRAM specific features:

- Component support for interface widths up to 64 bits (ECC is not available in DDR2 memories)

- Configurable data bus widths (doubles from 8, up to 64 bits)

- Support for 3 to 5 cycles of column address strobe (CAS) latency

- JEDEC-compliant DDR2 initialization support

### **Block Diagram**

## **Supported FPGA Families**

Xilinx<sup>®</sup> 7-Series

### **Development Tools**

Xilinx<sup>®</sup> ISE/EDK<sup>®</sup> 14.4 or later ModelSim<sup>®</sup> v10.1c or later Xilinx<sup>®</sup> ISIM 14.4 or later Xilinx<sup>®</sup> XST 14.4 or later

### Configuration

The DO-254 AXI 7 Series DDRx (Limited) 1.00a is configurable as shown below:

| Parameter Name   | Description                                                                                                             |

|------------------|-------------------------------------------------------------------------------------------------------------------------|

| C_ADDR_CMD_MODE  | This parameter is<br>used by the<br>controller to<br>calculate timing on<br>the memory<br>addr/cmd bus.                 |

| C_BANK_WIDTH     | Memory bank<br>address bus width.                                                                                       |

| C_BM_CNT_WIDTH   | This is the number<br>of bits required to<br>index a bank<br>machine and is<br>given by<br>ceil(log2(nBANK_M<br>ACHS)). |

| C_BURST_MODE     | This is the memory data burst length.                                                                                   |

| C_BURST_TYPE     | This is an option fo<br>the ordering of<br>accesses within a<br>burst.                                                  |

| C_CK_WIDTH       | This is the number<br>of CK/CK# outputs<br>to memory.                                                                   |

| C_CL             | This is the read CA<br>latency. The<br>available option is<br>frequency<br>dependent in the<br>MIG tool.                |

| C_COL_WIDTH      | This is the number<br>of memory column<br>address bits.                                                                 |

| C_CMD_PIPE_PLUS1 | This adds pipeline<br>stage between MC<br>and PHY.                                                                      |

| Parameter Name                | Description                                                                                                                                                |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C_CS_WIDTH                    | This is the number<br>of unique CS<br>outputs to<br>memory.                                                                                                |

| C_CKE_WIDTH                   | This is the number<br>of CKE outputs to<br>memory.                                                                                                         |

| C_CWL                         | This is the write<br>CAS latency. The<br>available option is<br>frequency<br>dependent in the<br>MIG tool.                                                 |

| C_DATA_BUF_ADDR_WIDT<br>H     | This is the bus<br>width of the<br>request tag passed<br>to the memory<br>controller. This<br>parameter is set to<br>5 for 4:1 mode and<br>4 for 2:1 mode. |

| C_PHY_CONTROL_MASTER<br>_BANK | This is the bank<br>number where<br>master<br>PHY_CONTROL<br>resides                                                                                       |

| C_DDR2_DQSN_ENABLE            | This enables<br>differential DQS for<br>DDR2.                                                                                                              |

| C_DM_WIDTH                    | This is the number<br>of data mask bits.                                                                                                                   |

| C_DQ_WIDTH                    | This is the memory<br>DQ bus width.                                                                                                                        |

| C_DQS_WIDTH                   | This is the memory<br>DQS bus width.                                                                                                                       |

| Parameter Name | Description                                                                                                               |

|----------------|---------------------------------------------------------------------------------------------------------------------------|

| C_DRAM_TYPE    | This is the<br>supported memory<br>standard for the<br>memory controller.                                                 |

| C_DRAM_WIDTH   | This is the DQ bus<br>width per DRAM<br>component.                                                                        |

| C_ECC          | This is the error<br>correction code,<br>available in 72-bit<br>data width<br>configurations.                             |

| C_ECC_TEST     | This feature is not<br>available.                                                                                         |

| C_NBANK_MACHS  | This is the number<br>of bank machines.<br>A given bank<br>machine manages<br>a single DRAM<br>bank at any given<br>time. |

| C_NCK_PER_CLK  | This is the number<br>of memory clocks<br>per clock.                                                                      |

| C_NCS_PER_RANK | This is the number<br>of unique CS<br>outputs per rank<br>for the PHY.                                                    |

| C_ORDERING     | This option<br>reorders received<br>requests to<br>optimize data<br>throughput and<br>latency.                            |

| Parameter Name      | Description                                                                                                                                             |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| C_IODELAY_HP_MODE   | This option enables<br>or disables the<br>IDELAY high-<br>performance<br>mode.                                                                          |

| C_BANK_TYPE         | IO bank type.                                                                                                                                           |

| C_DATA_IO_PRIM_TYPE | Primitive type for<br>IO bank.                                                                                                                          |

| C_IODELAY_GRP       | Design<br>implementation<br>constraint.                                                                                                                 |

| C_OUTPUT_DRV        | This is the DRAM<br>reduced output<br>drive option.                                                                                                     |

| C_REG_CTRL          | This is the option<br>for DIMM or<br>unbuffered DIMM<br>selection.                                                                                      |

| C_RTT_NOM           | This is the nominal<br>ODT value. The<br>"DISABLED" choice<br>cannot be<br>configured in the<br>MIG GUI, and can<br>only be set in the<br>MHS file.     |

| C_RTT_WR            | This is the dynamic<br>ODT write<br>termination used in<br>multiple-RANK<br>designs. For single-<br>component<br>designs, RTT_WR<br>should be disabled. |

| Parameter Name | Description                                                                        |

|----------------|------------------------------------------------------------------------------------|

| с_тск          | This is the memory<br>tCK clock period<br>(ps).                                    |

| С_ТСКЕ         | This is the CKE<br>minimum pulse.                                                  |

| C_TFAW         | This is the<br>minimum interval<br>of four active<br>commands.                     |

| C_TPRDI        | This is the periodic read.                                                         |

| C_TRAS         | This is the<br>minimum ACTIVE-<br>to-PRECHARGE<br>period for memory.               |

| C_TRCD         | This is the ACTIVE-<br>to-READ or –<br>WRITE command<br>delay.                     |

| C_TREFI        | This is the average<br>periodic refresh<br>interval for<br>memory.                 |

| C_TRFC         | This is the<br>REFRESH-to-ACTIVE<br>or REFRESH-to-<br>REFRESH command<br>interval. |

| C_TRP          | This is the<br>PRECHARGE<br>command period.                                        |

| C_TRRD         | This is the ACTIVE-<br>to-ACTIVE<br>minimum<br>command period.                     |

| Parameter Name  | Description                                                                                                                                                    |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C_TRTP          | This is the READ-to-<br>PRECHARGE<br>command delay.                                                                                                            |

| C_TWTR          | This is the WRITE-<br>to-READ command<br>delay.                                                                                                                |

| C_TZQI          | This is the timing<br>window to perform<br>the ZQCL command<br>in DDR3 SDRAM.                                                                                  |

| C_TZQCS         | This is the timing<br>window to perform<br>the ZQCS command<br>in DDR3 SDRAM.                                                                                  |

| C_CAL_WIDTH     | This is the calibration width.                                                                                                                                 |

| C_RANKS         | This is the number of ranks.                                                                                                                                   |

| C_ODT_WIDTH     | This is the number<br>of ODT outputs to<br>memory.                                                                                                             |

| C_ROW_WIDTH     | This is the DRAM<br>component<br>address bus width.                                                                                                            |

| C_BYTE_LANES_BO | Defines the byte<br>lanes being used in<br>a given I/O bank. A<br>"1" in a bit position<br>indicates a byte<br>lane is used, and a<br>"0" indicates<br>unused. |

| Parameter Name  | Description                                                                                                                                                    |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C_BYTE_LANES_B1 | Defines the byte<br>lanes being used in<br>a given I/O bank. A<br>"1" in a bit position<br>indicates a byte<br>lane is used, and a<br>"0" indicates<br>unused. |

| C_BYTE_LANES_B2 | Defines the byte<br>lanes being used in<br>a given I/O bank. A<br>"1" in a bit position<br>indicates a byte<br>lane is used, and a<br>"0" indicates<br>unused. |

| C_BYTE_LANES_B3 | Defines the byte<br>lanes being used in<br>a given I/O bank. A<br>"1" in a bit position<br>indicates a byte<br>lane is used, and a<br>"0" indicates<br>unused. |

| C_BYTE_LANES_B4 | Defines the byte<br>lanes being used in<br>a given I/O bank. A<br>"1" in a bit position<br>indicates a byte<br>lane is used, and a<br>"0" indicates<br>unused. |

| Parameter Name | Description                                                                                                                                                                                           | Parameter Name   | Description                                                                                                                                                                                                                                                                                            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C_DATA_CTL_BO  | Defines mode of<br>use of byte lanes in<br>a given I/O bank. A<br>"1" in a bit position<br>indicates a byte<br>lane is used for<br>data, and a "0"<br>indicates it is used<br>for<br>address/control. | C_DATA_CTL_B3    | Defines mode of<br>use of byte lanes<br>a given I/O bank.<br>"1" in a bit positi<br>indicates a byte<br>lane is used for<br>data, and a "0"<br>indicates it is use<br>for<br>address/control.                                                                                                          |

| C_DATA_CTL_B1  | Defines mode of<br>use of byte lanes in<br>a given I/O bank. A<br>"1" in a bit position<br>indicates a byte<br>lane is used for<br>data, and a "0"<br>indicates it is used<br>for<br>address/control. | C_DATA_CTL_B4    | Defines mode of<br>use of byte lanes<br>a given I/O bank.<br>"1" in a bit positi<br>indicates a byte<br>lane is used for<br>data, and a "0"<br>indicates it is use<br>for<br>address/control.                                                                                                          |

| C_DATA_CTL_B2  | Defines mode of<br>use of byte lanes in<br>a given I/O bank. A<br>"1" in a bit position<br>indicates a byte<br>lane is used for<br>data, and a "0"<br>indicates it is used<br>for<br>address/control. | C_PHY_O_BITLANES | 12-bit parameter<br>per byte lane use<br>to determine wh<br>I/O locations are<br>used to generate<br>the necessary PH<br>structures. This<br>parameter is<br>provided as per<br>bank. Except CKE<br>ODT, and RESET<br>pins, all Data and<br>Address/Control<br>pins are consider<br>for this parameter |

generation.

| Parameter Name   | Description                                                                                                                                                                                                                                                                                                                   |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C_PHY_1_BITLANES | 12-bit parameter<br>per byte lane used<br>to determine which<br>I/O locations are<br>used to generate<br>the necessary PHY<br>structures. This<br>parameter is<br>provided as per<br>bank. Except CKE,<br>ODT, and RESET<br>pins, all Data and<br>Address/Control<br>pins are considered<br>for this parameter<br>generation. |

| C_PHY_2_BITLANES | 12-bit parameter<br>per byte lane used<br>to determine which<br>I/O locations are<br>used to generate<br>the necessary PHY<br>structures. This<br>parameter is<br>provided as per<br>bank. Except CKE,<br>ODT, and RESET<br>pins, all Data and<br>Address/Control<br>pins are considered<br>for this parameter<br>generation. |

| Parameter Name | Description                                                                                                                   |

|----------------|-------------------------------------------------------------------------------------------------------------------------------|

| C_CK_BYTE_MAP  | Bank and byte lane<br>location<br>information for the<br>CK/CK#. An 8-bit<br>parameter is<br>provided per pair<br>of signals. |

| C_ADDR_MAP     | Bank and byte lane<br>position<br>information for the<br>address. 12-bit<br>parameter<br>provided per pin.                    |

| C_BANK_MAP     | Bank and byte lane<br>position<br>information for the<br>bank address.                                                        |

| C_CAS_MAP      | Bank and byte lane<br>position<br>information for the<br>CAS command.                                                         |

| C_CKE_MAP      | Bank and byte lane<br>position<br>information for the<br>Clock Enable.                                                        |

| C_ODT_MAP      | Bank and byte lane<br>position<br>information for the<br>On-Die<br>Termination.                                               |

| C_CKE_ODT_AUX  | This enables the aux_out signal.                                                                                              |

| Parameter Name | Description                                                                                                     |

|----------------|-----------------------------------------------------------------------------------------------------------------|

| C_CS_MAP       | Bank and byte lane<br>position<br>information for the<br>chip select. 1 2-bit<br>parameter<br>provided per pin. |

| C_PARITY_MAP   | Bank and byte lane<br>position<br>information for the<br>parity bit. Parity bit<br>exists for RDIMMs<br>only.   |

| C_RAS_MAP      | Bank and byte lane<br>position<br>information for the<br>RAS command.                                           |

| C_WE_MAP       | Bank and byte lane<br>position<br>information for the<br>WE command.                                            |

| C_DQS_BYTE_MAP | Bank and byte lane<br>position<br>information for the<br>strobe.                                                |

| C_DATA0_MAP    | Bank and byte lane<br>position<br>information for the<br>data bus.                                              |

| C_DATA1_MAP    | Bank and byte lane<br>position<br>information for the<br>data bus.                                              |

| C_DATA2_MAP    | Bank and byte lane<br>position<br>information for the<br>data bus.                                              |

| Parameter Name | Description                                                        |

|----------------|--------------------------------------------------------------------|

| C_DATA3_MAP    | Bank and byte lane<br>position<br>information for the<br>data bus. |

| C_DATA4_MAP    | Bank and byte lane<br>position<br>information for the<br>data bus. |

| C_DATA5_MAP    | Bank and byte lane<br>position<br>information for the<br>data bus. |

| C_DATA6_MAP    | Bank and byte lane<br>position<br>information for the<br>data bus. |

| C_DATA7_MAP    | Bank and byte lane<br>position<br>information for the<br>data bus. |

| C_DATA8_MAP    | Bank and byte lane<br>position<br>information for the<br>data bus. |

| C_DATA9_MAP    | Bank and byte lane<br>position<br>information for the<br>data bus. |

| C_DATA10_MAP   | Bank and byte lane<br>position<br>information for the<br>data bus. |

| C_DATA11_MAP   | Bank and byte lane<br>position<br>information for the<br>data bus. |

| Parameter Name   | Description                                                         | Para  |

|------------------|---------------------------------------------------------------------|-------|

| C_DATA12_MAP     | Bank and byte lane<br>position<br>information for the<br>data bus.  | C_SII |

| C_DATA13_MAP     | Bank and byte lane<br>position<br>information for the<br>data bus.  | C_RE  |

| C_DATA14_MAP     | Bank and byte lane<br>position<br>information for the<br>data bus.  | C_US  |

| C_DATA15_MAP     | Bank and byte lane<br>position<br>information for the<br>data bus.  | C_US  |

| C_DATA16_MAP     | Bank and byte lane<br>position<br>information for the<br>data bus.  | C_US  |

| C_MASKO_MAP      | Bank and byte lane<br>position<br>information for the<br>data mask. |       |

| C_MASK1_MAP      | Bank and byte lane<br>position<br>information for the<br>data mask. | C_US  |

| C_SLOT_0_CONFIG  | This is the rank mapping for slot 1.                                |       |

| C_SLOT_1_CONFIG  | This is the rank mapping for slot 2.                                |       |

| C_MEM_ADDR_ORDER | This is the memory address order.                                   |       |

| Parameter Name        | Description                                                                                                                                                              |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C_SIM_BYPASS_INIT_CAL | This simulation<br>only parameter is<br>used to speed up<br>simulations.                                                                                                 |

| C_REFCLK_FREQ         | This is the<br>reference clock<br>frequency for<br>IODELAYCTRLs. This<br>can be set to 200.0<br>for any speed<br>grade device.                                           |

| C_USE_CS_PORT         | This enables the use of the CS port.                                                                                                                                     |

| C_USE_DM_PORT         | This is the enable<br>data mask option<br>used during<br>memory write<br>operations.                                                                                     |

| C_USE_ODT_PORT        | This enables the<br>use of the ODT<br>port. This<br>parameter cannot<br>be configured in<br>the MIG GUI, and<br>can only be set in<br>the MHS file.<br>Defaults to 1.    |

| C_USE_EXTERNAL_XADC   | This instantiates or<br>uses external<br>XADC. This<br>parameter cannot<br>be configured in<br>the MIG GUI, and<br>can only be set in<br>the MHS file.<br>Defaults to 0. |

| Parameter Name                  | Description                                                                                                                                                                                                                    | Parameter Name                               | Description                                                                                                                                                                                                                        |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C_USE_EXTERNAL_IODELAY<br>_CTRL | This enables<br>"iodelay_ctrl_rdy_i<br>" when set to 1.                                                                                                                                                                        | C_S_AXI_SUPPORTS_NARR<br>OW_BURST            | This parameter<br>adds logic blocks to<br>support narrow AX                                                                                                                                                                        |

|                                 | This is the width of<br>ID signals for every<br>channel. This value<br>is automatically<br>computed in EDK<br>designs. This<br>parameter cannot<br>be configured in<br>the MIG GUI, and<br>can only be set in<br>the MHS file. |                                              | transfers. It is<br>required if any<br>master connected<br>to the memory<br>controller issues<br>narrow bursts. This<br>parameter is<br>automatically set if<br>the AXI data width<br>is smaller than the<br>recommended<br>value. |

| C_S_AXI_ADDR_WIDTH              | Defaults to 4.<br>This is the width of<br>address read and<br>address write<br>signals. EDK<br>designs are limited<br>to 32.                                                                                                   | C_RD_WR_ARB_ALGORITH<br>M<br>C_S_AXI_REG_EN0 | This parameter<br>indicates the<br>Arbitration<br>algorithm scheme.<br>This parameter<br>instantiates                                                                                                                              |

|                                 | This is the width of<br>data signals. The<br>recommended<br>width is 8x the<br>memory data<br>width. The width                                                                                                                 | C_S_AXI_REG_EN1                              | register slices<br>before upsizer.<br>This parameter<br>instantiates<br>register slices after<br>upsizer.                                                                                                                          |

|                                 | can be smaller, but<br>not greater than 8x<br>the memory data<br>width.                                                                                                                                                        |                                              |                                                                                                                                                                                                                                    |

| Parameter Name       | Description          | Par | rameter Name      | Description          |

|----------------------|----------------------|-----|-------------------|----------------------|

| C_S_AXI_HIGHADDR     | This parameter       | C_S | _AXI_HIGHADDR     | This parameter       |

|                      | specifies the high   |     |                   | specifies the high   |

|                      | address for the      |     |                   | address for the      |

|                      | memory mapped        |     |                   | memory mapped        |

|                      | slave interface.     |     |                   | slave interface.     |

|                      | Address requests     |     |                   | Address requests     |

|                      | received above this  |     |                   | received above thi   |

|                      | value wrap back to   |     |                   | value wrap back to   |

|                      | the base address.    |     |                   | the base address.    |

|                      | The base/high        |     |                   | The base/high        |

|                      | address together     |     |                   | address together     |

|                      | defines the          |     |                   | define the           |

|                      | accessible size of   |     |                   | accessible size of   |

|                      | the memory. This     |     |                   | the memory. This     |

|                      | accessible size      |     |                   | accessible size      |

|                      | must be a power of   |     |                   | must be a power o    |

|                      | 2. Additionally, the |     |                   | 2. Additionally, the |

|                      | base/high address    |     |                   | base/high address    |

|                      | pair must be         |     |                   | pair must be         |

|                      | aligned to a         |     |                   | aligned to a         |

|                      | multiple of the      |     |                   | multiple of the      |

|                      | accessible size. The |     |                   | accessible size. The |

|                      | minimum              |     |                   | minimum              |

|                      | accessible size is   |     |                   | accessible size is   |

|                      | 4096 bytes.          |     |                   | 4096 bytes.          |

| C_S_AXI_CTRL_ADDR_WI | DT This parameter    | C_S | _AXI_CTRL_ADDR_WI | DT This parameter    |

| н                    | specifies the width  | н   |                   | specifies the width  |

|                      | of AXI 4 Lite        |     |                   | of AXI 4 Lite        |

|                      | address bus.         |     |                   | address bus.         |

| C_S_AXI_CTRL_DATA_WI | DT This parameter    | C_S | _AXI_CTRL_DATA_WI | DT This parameter    |

| н                    | specifies the width  | н   |                   | specifies the width  |

|                      | of AXI 4 Lite data   |     |                   | of AXI 4 Lite data   |

|                      | buses.               |     |                   | buses.               |

| Parameter Name              | Description                                                                                                                                                                                        |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C_ECC_ONOFF_RESET_VAL<br>UE | This parameter<br>specifies the ECC<br>on/off value at<br>startup/reset. This<br>parameter cannot<br>be configured in<br>the MIG GUI, and<br>can only be set in<br>the MHS file.<br>Defaults to 1. |

#### Assumptions

**Assumption 1**: The integrator will develop a full set of DO-254 artifacts to reflect the objectives, activities, and lifecycle data related to the system/safety, implementation, target test, acceptance test, production transition aspects, related validation and verification, configuration management, process assurance, and certification liaison aspects of the system/LRU.

**Assumption 2**: The objectives, activities and lifecycle data related specifically to the DO-254 AXI 7 Series DDRx (Limited) Core will be provided to the Integrator for inclusion into their overall certification package.

**Assumption 3**: Place and route, clock frequency, and parameter selection decisions related to the IP core will have an impact on critical areas such as timing. These decisions and the verification of these implementation decisions will be the responsibility of the integrator.

**Assumption 4**: All objectives related to the building, integration and production (including

Production Testing — ATP) of the system/LRU will be the responsibility of the integrator.

**Assumption 5**: Objectives related to hardware components other than the DO-254 AXI 7 Series DDRx (Limited) Core are the responsibility of the integrator.

Assumption 6: The integrator will develop all DO-254 artifacts that are related to the integration and testing of the DO-254 AXI 7 Series DDRx (Limited) Core in their system.

**Assumption 7**: The integrator will perform implementation objectives related to the target hardware, including the integral process objectives, to verify the timing and other critical parameters of the DO-254 AXI 7 Series DDRx (Limited) Core.

**Assumption 8**: The applicant is responsible for communicating with their Certification Authority relative to the implementation of the DO-254 AXI 7 Series DDRx (Limited) Core into their system.

**Assumption 9**: Compliance with the objectives related to system (and safety-related) requirements allocated to the hardware will be the responsibility of the integrator. The requirement to feed all IP derived requirements to the System/Safety Process will be the responsibility of the integrator. The integrator will be required to generate hardware requirements allocated from the system requirements that exercise the DO-254 AXI 7 Series DDRx (Limited) Core at the system level.

**Assumption 10**: The integrator is required to include a clock timing constraint for this DO-254 AXI 7 Series DDRx (Limited) Core. This clock timing constraint will define the clock rate at

which the IP core will operate. It is recommended that the integrator defines this constraint in the UCF file. The integrator typically would also include (at a minimum, but not limited to) pinout constraints, I/O electrical standards, etc. An example UCF file will be provided in Chapter 3 of the 10116-UG, but it is for reference only.

**Assumption 11**: The integrator is not required to rerun any elemental analysis (code coverage). Code coverage results indicate that all configurations required to attain 100% coverage are tested.

Assumption 12: Some testing of the DO-254 AXI 7 Series DDRx (Limited) Core was done on a test board, the integrator is responsible for complete IP black box testing in his system. In order to accomplish this black box testing, the integrator is recommended to design his PCB to have access to at least XX (number defined in 10116-UG) spare FPGA pins that can be connected to a logic analyzer. If the integrator chooses to do post place and route simulation on their system as an additional validation, Logicircuit will provide the necessary files for the DO-254 AXI 7 Series DDRx (Limited) Core.

# **Revision History**

|          |                    |            | Subversion<br>repository |

|----------|--------------------|------------|--------------------------|

| Revision | Reason/Description | Date       | revision                 |

| -        | Initial Release    | 08/29/2014 | 134                      |