December 13, 2012, Revision -

## **General Description**

The AXI Master Lite DO-254 Certifiable Data Package is made up of the artifacts produced by applying the DO-254 lifecycle to the Xilinx<sup>®</sup> AXI Master Lite IP and an encrypted version of the source code. This includes the following completed documents:

- Plan for Hardware Aspects of Certification

- Hardware Validation and Verification

Plan

- Hardware Configuration Management Plan

- Hardware Design Plan

- Hardware Process Assurance Plan

- Hardware Validation and Verification

Standard

- Hardware Requirements Standard

- Hardware Design Standard

- Hardware Requirements Document

- Hardware Design Document

- Hardware Elemental Analysis Results

- Hardware Configuration Index (includes Hardware Lifecycle Environment Configuration Index)

- Hardware Test Procedures

- Hardware Verification Results

- Hardware Elemental Analysis Results

- Hardware Requirements Traceability

Matrix

- Hardware Accomplishment Summary

The above documents are available for certification efforts, however not all documents are included in the delivery package.

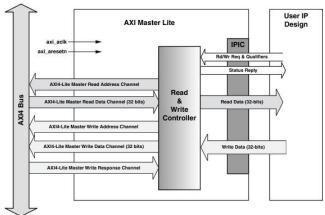

The AXI Master Lite is an AXI4-compatible LogiCORE<sup>™</sup> IP product. It provides an interface between a user-created IP core and an AXI4-Lite interface. The AXI4-Lite Master IP supports AXI4-Lite-compatible bus mastering operations which are single 32-bit wide read or write data transfers.

#### **Safety Features**

The DO-254 AXI Master Lite IP includes the following safety signals:

- The md\_error signal indicates that the master detected an error. This bit is sticky once set, and is only cleared by a hardware reset.

- The Bus2IP\_Mst\_Error signal indicates an error response was received from the AXI4 bus during the requested transfer.

## Features

- AXI4-Lite Master interface

- Fixed 32-bit data width

- Supports single beat read and write data transfers of up to 4 bytes (32bits)

- IPIC back-end interface for PLBV46 Master Single migration

## **Block Diagram**

Figure 1: AXI Master Lite Block Diagram

Xilinx<sup>®</sup> 7-Series and Spartan<sup>®</sup>-6

#### **Development Tools**

Xilinx<sup>®</sup> ISE/EDK<sup>®</sup> 13.4 or later ModelSim<sup>®</sup> v10.1b or later (models required) Xilinx<sup>®</sup> ISIM 13.4 or later (no models required) Xilinx<sup>®</sup> XST 13.4 or later Precision Synthesis 2012b or later

## Assumptions

Assumption 1: The integrator will develop a full set of DO-254 artifacts to reflect the objectives, activities, and lifecycle data related to the system/safety, implementation, target test, acceptance test, production transition aspects, related validation and verification, configuration management, process assurance, and certification liaison aspects of the system/LRU. The objectives, activities and lifecycle data related specifically to the DO-254 AXI Master Lite IP Core 1.00a will be provided to the Integrator for inclusion into their overall certification package.

**Assumption 2**: Place and route, clock frequency, and parameter selection decisions related to the IP core will have an impact on critical areas such as timing. These decisions and the verification of these implementation decisions will be the responsibility of the integrator.

**Assumption 3**: Logicircuit will coordinate with the Certification Authority related only to DO-254 compliance with the DO-254 AXI Master Lite IP Core 1.00a.

**Assumption 4**: All objectives related to the building, integration and Production (including Production Testing - ATP) of the system/LRU will be the responsibility of the integrator.

**Assumption 5**: Objectives related to hardware components other than the DO-254 AXI Master Lite IP Core 1.00a are the responsibility of the integrator.

**Assumption 6**: The integrator will develop all DO-254 artifacts that are related to the integration and testing of the DO-254 AXI Master Lite IP Core 1.00a in their system.

**Assumption 7**: The integrator will perform implementation objectives related to the target hardware, including the integral process objectives, to verify the timing and other critical parameters of the DO-254 AXI Master Lite IP Core 1.00a.

Assumption 8: The applicant is responsible for communicating with their Certification Authority relative to the implementation of the DO-254 AXI Master Lite IP Core 1.00a into their system.

Assumption 9: Compliance with the objectives related to system (and safety-related) requirements allocated to the hardware will be the responsibility of the integrator. The requirement to feed all IP derived requirements to the System/Safety Process will be the responsibility of the integrator. The integrator will be required to generate hardware requirements allocated from the system requirements that exercise the DO-254 AXI Master Lite IP Core 1.00a at the system level.

Assumption 10: The integrator is required to include a clock timing constraint for this DO-254 AXI Master Lite IP Core 1.00a. This clock timing constraint will define the clock rate at which the IP core will operate. It is recommended that the integrator define this constraint in the UCF file. The integrator typically would also include

(at a minimum, but not limited to) pinout constraints, I/O electrical standards, etc. An example UCF file will be provided in 10110-UG, but it is for reference only.

Assumption 11: The integrator is not required to rerun any elemental analysis (code coverage). Code coverage results will indicate that all configurations required to attain 100% coverage are tested.

Simulation validation for the DO-254 AXI Master Lite IP Core 1.00a is being done on a test board. The integrator must revalidate a portion of this simulation on the integrator's target. Logicircuit will provide the files and data necessary to perform this revalidation in 10110-UG.

# In order to accomplish this revalidation, the integrator is required to design his PCB to have access to at least 22 spare FPGA pins that can be connected to a logic analyzer.

If the integrator chooses to do post place and route simulation on their system as an additional validation (again, this would only be a portion of Logicircuit's simulation), Logicircuit will provide the necessary files for the DO-254 AXI Master Lite IP Core 1.00a.